|

|||||||

|

|||||||

|

|

|||||||

|

|||||||

|

| FM25CL64-DG资料 | |

|

|

FM25CL64-DG PDF Download |

|

File Size : 116 KB

Manufacturer:RAMTRON Description:BURST CONFIGURATION COMMAND: The Program Burst Configuration Register command is used to program the burst configuration register. The burst configuration register determines several parameters that control the read operation of the device. Bit B15 determines whether synchronous burst reads are enabled or asynchronous reads are enabled. Since the page read operation is an asynchronous operation, bit B15 must be set for asynchronous reads to enable the page read feature. Bit B14 determines whether a four-word page or an eight-word page will be used. The rest of the bits in the burst configuration register are used only for the burst read mode. Bits B13 - B11 of the burst configuration register determine the clock latency for the burst mode. The latency can be set to two, three, four, five or six cycles. The clock latency versus input clock frequency table is shown on page 20. The Burst Read Waveform as shown on page 31 illustrates a clock latency of four; the data is output from the device four clock cycles after the first valid clock edge following the high-to-low AVD edge. The B10 bit of the configuration register determines the polarity of the WAIT signal. The B9 bit of the burst configuration register determines the number of clocks that data will be held valid (see Figure 4). The Hold Data for 2 Clock Cycles Read Waveform is shown on page 31. The clock latency is not affected by the value of the B9 bit. The B8 bit of the burst configuration register deter- mines when the WAIT signal will be asserted. When synchronous burst reads are enabled, a linear burst sequence is selected by setting bit B7. Bit B6 selects whether the burst starts and the data output will be relative to the falling edge or the rising edge of the clock. Bits B2 - B0 of the burst configuration register determine whether a continuous or fixed-length burst will be used and also determine whether a four-, eight- or sixteen-word length will be used in the fixed-length mode. When a four-, eight- or sixteen-word burst length is selected, Bit B3 can be used to select whether burst accesses wrap within the burst length boundary or whether they cross word length boundaries to perform linear accesses (see Table 5). All other bits in the burst configuration register should be programmed as shown on page 20. The default state (after power-up or reset) of the burst configuration register is also shown on page 20. |

|

| 相关型号 | |

| ◆ MF2410F1.000TM | |

| ◆ MF2410F2.000TM | |

| ◆ 0805-125 1.25A 6V | |

| ◆ 0805-110 1.1A 6V | |

| ◆ 0805-100 1A 6V | |

| ◆ 0805-075 750MA 6V | |

| ◆ 0805-050 500MA 6V | |

| ◆ 0805-035 350MA 6V | |

| ◆ 0805-020 200MA 9V | |

| ◆ 0805-010 100MA 15V | |

| 1PCS | 100PCS | 1K | 10K | |||||||||||||||||||||||||||

| 价 格 | ||||||||||||||||||||||||||||||

|

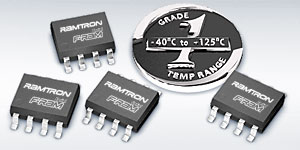

型 号:FM25CL64-DG 厂 家:RAMTRON 封 装:QFN 批 号:08+ 数 量:785 说 明:

64Kbit位非易失性铁电存储器 完备的写保护机制 低功耗

• 汽车级温度:-40℃~+125℃ |

||||||||||||||||||||||||||||||

|

运 费:运费到付10.00元(快递)20.00元(顺风) 所在地:深圳 新旧程度:原装 |

||||||||||||||||||||||||||||||

| 联系人:欧阳先生 |

| 电 话:0755-83295252,83294949,82565501,82565401 |

| 手 机: |

| QQ:104735486 |

| MSN: |

| 传 真:0755-82565401 |

| EMail:oyzf8888@qq.com |

| 公司地址: 深圳市福田区华强北新亚洲电子商城一期五楼526房间 |

|

订购须知: 由于电子行情瞬息万变,请在订购前询问清楚,跟本公司业务员确认好价格,货物情况后再下单。 以免出现不必要误会。 【售后服务】:属于产品质量问题,其余在不拆包装不上锡情况下可包退换!如有其他问题需退换,请在一周内联系我司。

我们的产品还在不断更新中!产品繁多,未能尽列,如买家找不到的元件可以与我们联系。欢迎您的咨询!

|